Senior Design: Digital ASIC Fabrication

Designing a chip framework that supports and connects smaller ASIC

projects.

details

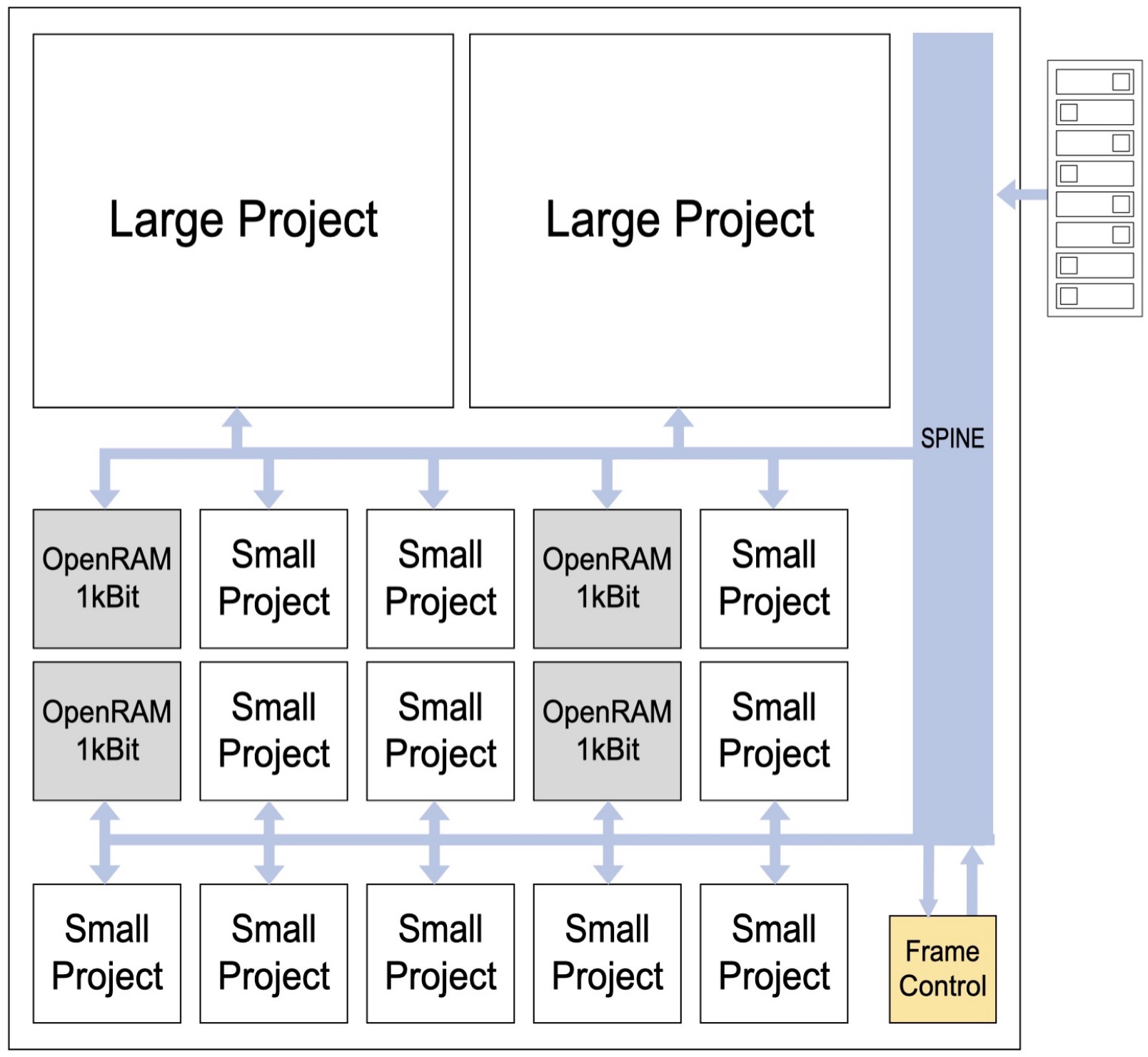

Our project aims to build and silicon-prove a chip framework that

will support a continuous cycle of chip designs, or “tape outs,”

ready for fabrication. The project’s overall goal is to give

interested students experience in chip design and fabrication. The

framework we design will provide space for multiple small projects

and the ability to run each independently. The project modules will

be created by a co-curricular team of students ranging from freshmen

to seniors. By breaking the design process into smaller, less

complex subprojects, students will be able to complete modules

within a semester. Each module will be fabricated and synthesized as

a hard macro that can be used in our framework.

This project is part of Iowa State's Electrical and Computer

Engineering Senior Design program. You can view my team's official

website

here.

Languages: Verilog, C

Tools: Linux, GTKWave, KLayout

Technologies: Caravel SoC, SkyWater Open Source PDK

Tools: Linux, GTKWave, KLayout

Technologies: Caravel SoC, SkyWater Open Source PDK